Modos de operação

Suporte para sistemas operacionais

Para suporte de sistemas operacionais, o processador possui modos de execução e exceção dedicados. Além disso, o fabricante do chip pode incluir um timer em hardware de 24 bits chamado Systick (System Tick Timer) e outros recursos como: unidade de proteção de memória (MMU), vetores de interrupção realocáveis e shadowed stack.

Modos de operação

Existem dois modos de operação: Thread e Handler. O modo Thread é definido quando a operação do processador é iniciada (modo de Reset). O processador entra em modo Handler quando ocorre uma exceção (interrupção). Quando o contexto é restabelecido, o processador retorna para o estado Thread.

Shadowed stack

Existem duas pilhas, denominadas Main e Process Stack Pointer. O motivo dessa duplicação é o seguinte: No modo de operação Handler, a pilha Main (MSP) é utilizada. Já no modo Thread, essa definição é realizada via configuração do registrador de controle do processador. Esse recurso permite que tarefas de um sistema operacional não sejam corrompidas pela aplicação.

Modos de execução

Além dos modos de operação, existem dois estados de execução: Privilegiado e Não Privilegiado. O estado de privilégio significa que o código de aplicação pode executar todas as instruções disponíveis e acessar todos os recursos de hardware, por exemplo, acessar o registrador de controle do processador. O modo de operação Handlersempre é executado com privilégio. Já o modo não privilegiado tem as seguintes restrições:

Pode ter o acesso restrito para alguns periféricos.

Não pode acessar o Systick, NVIC, e os registradores de controle do processador.

Algumas instruções tem a execução limitada (MSR e MRS) e outras não podem ser utilizadas (CPS – controle de interrupção).

Suporte à exceções

Possui um sistema flexível para controlar interrupções, denominado NVIC. Tal sistema tem suporte para 32 fontes de interrupção, com funções de priorização (4 níveis) e ativação.

Ao todo, existem seis tipos de exceções mais o Reset [1].

Hardware fault: Tem a maior prioridade, sendo causada por algum erro, por exemplo, ao executar uma instrução indefinida, ou realizar uma operação de Load em um endereço que não está alinhado.

NMI: Interrupção gerada por periféricos ou via software. Não pode ser mascarada.

IRQ: Interrupção gerada por periféricos ou via software.

SVCall: Exceção gerada pela execução da instrução SVC.

PendSV: Requisição de interrupção feita pelo sistema (SO). Usada para trocar o contexto, isto é, atender a chamada SVC.

Systick: Exceção gerada quando a contagem do Systick chega ao valor zero.

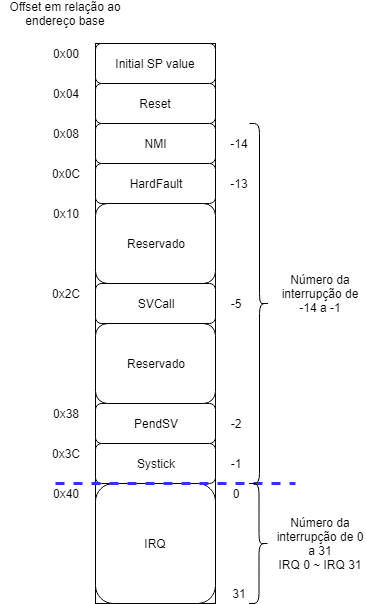

Toda exceção possui um número de identificação, um endereço na tabela de interrupções e uma prioridade de execução. Na tabela de interrupções, os primeiros 16 endereços possuem funções específicas, sendo o restante dependente do fabricante do microcontrolador. A primeira posição é destinada para indicar o endereço da região de stack. A segunda, para indicar o ponto de entrada da aplicação.

A latência de interrupção é de 15 ciclos de clock e se mantém constante – zero jitter – independente das instruções executadas. O único fator que altera esse tempo é a configuração de wait states no acesso à memória [].

As ISRs não necessitam de instruções para o ponto de entrada, evitando a sobrecarga/aumento das operações. Isso ocorre devido a operação de carga dos registradores – hardware stacking – na pilha durante a troca de contexto [1].

Latência: Ciclos de clock necessários para que o processador responda ao evento de interrupção.

Jitter: Variações que podem ocorrer no tempo tomado para uma interrupção.

Modos de sleep

Considerando aplicações de baixo consumo, o processador tem suporte para dois modos de sleep: normal e profundo (deep). O comportamento desses modos é dependente do chip (fabricante). Podem ser adicionados modos específicos de baixo consumo (ou, power saving), totalizado 4 modos de sleep.

Outras propriedades que resultam em redução de consumo são destacadas a seguir:

Wakeup: Possui módulo que permite monitorar interrupções em modo sleep. Quando ocorre uma exceção o processador retoma o estado de execução para tratar a ISR.

Sleep-on-exit: Permite que o processador retorne para o modo de sleep quando uma ISR é tratada.

Last updated