Sistema de interconexão

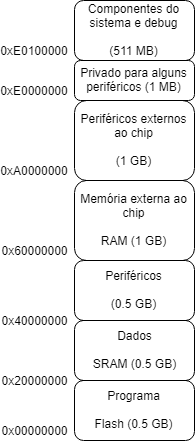

Todos os barramentos internos são de 32 bits. Devido a isso, o espaço de endereçamento é de 4 GB. O mapa de memória do processador separa o espaço de endereçamento em múltiplas regiões, sendo representadas por diferentes tecnologias de memória e atributos. Assim sendo, pode-se dizer que a arquitetura é baseada no modelo de von Neumann, pois todas as regiões são acessadas pelo mesmo barramento.

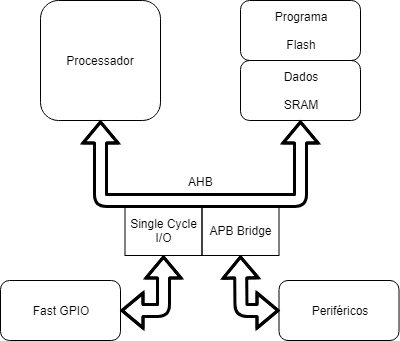

Todos os módulos do sistema são conectados seguindo padrão de interconexão chamado AMBA [1]. Essa arquitetura de interconexão mantém o processador e a memória conectados em um barramento de alta velocidade, denominado barramento do sistema.

O barramento do sistema é estruturado conforme o protocolo AHB Lite (do inglês, Advanced High Performance Bus), permitindo transferências de dados de 8, 16 e 32 bits. Além disso, é possível configurar ciclos de espera – wait states – para acesso à memória.

Wait state: Para operações de acesso à memória que duram mais que um ciclo de clock, o processador deve aguardar até que o procedimento seja finalizado. Isso é feito adicionado ciclos de espera, denominado wait state.

Os periféricos são conectados em outro barramento, chamado APB [1]. O APB é conectado ao barramento do sistema através de um módulo de interface (Bus Bridge). Com isso, o APB pode operar em frequências diferentes do barramento do sistema. Cabe ressaltar que os periféricos são mapeados em memória.

Além disso, existe um barramento dedicado para operações rápidas, chamado Single Cycle I/O Interface. Nesse barramento, os periféricos de I/O podem são acessados em um único ciclo de clock [1]. Nesse contexto, pode ser considerada uma arquitetura híbrida (Harvard limitada), pois possui um barramento dedicado para acessar registradores de periféricos de modo mais rápido [2].

Last updated